How can I use the Status System to make sure that an operation is complete?

Measuring a low frequency with a reciprocal counter, performing a swept-sine measurement with a dynamic signal analyzer or spectrum analyzer, and scanning through a list of channels with a data acquisition system (to mention a few of the most outstanding examples), all share a common source of trouble. These operations take time. Any operation that follows (such as reading the data resulting from the operations) must be delayed to insure that it doesn't interrupt the ongoing measurement, or cause a timeout. A seemingly reasonable solution would be to introduce delays or wait periods after the offending operation. But this poses a problem: How do you determine the time needed for the operation to complete without adding unnecessary delays to your program? A better solution is found in proper use of the Status System.

Most instruments have a set of registers that report the status of the instrument including various errors. These can be used to assert an SRQ (service request) and thus indicate to the controller that an event of interest has occurred or that certain condition exists.

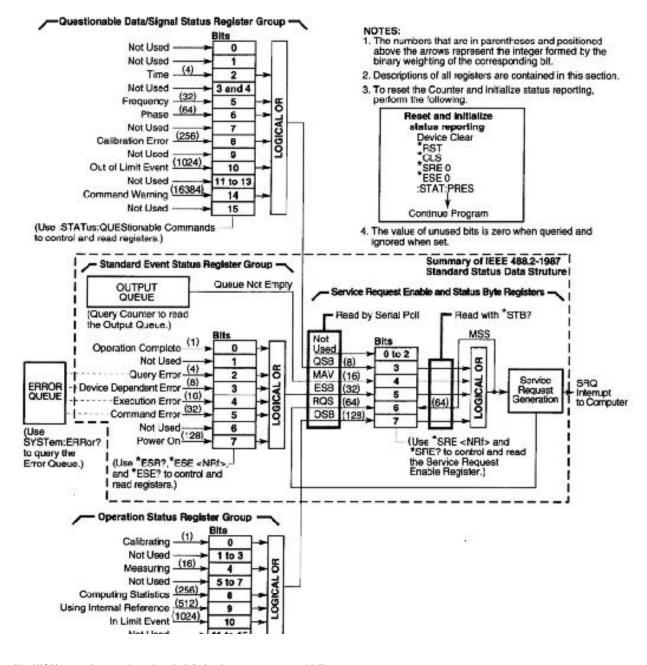

For the purpose of studying the status system, we will use the 53131A counter. However, the concepts are applicable to most instruments. The following is a diagram of the 53131A Status System.

```

(Use :STATus:OPERation Commands to control and read registers.)

```

Our main interest will be the output queue, the standard event register and the status byte. Before we can program the status register we must first clear it with the command \*CLS.

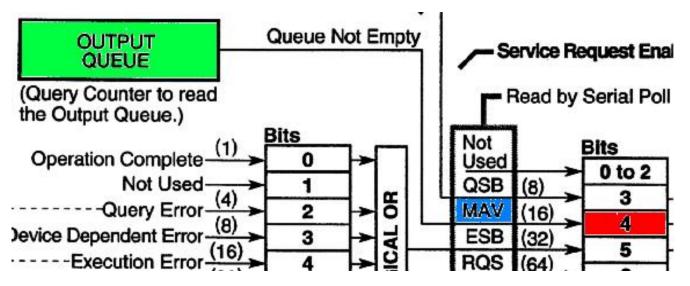

The output queue can have one of two conditions, it can have data in it as a result of a previous operation or not. If there is data in the output queue, this is indicated by setting bit four of the status byte (MAV -- message available).

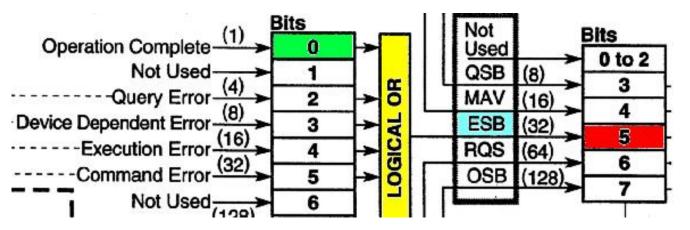

Each register is paired up with an enable register (not shown in these illustrations). For example, the standard event register has a corresponding standard event enable register. Since our interest is in bit zero of the standard event register, we must enable it by placing a one in the corresponding bit of the standard event enable register. This is done by writing a decimal value equivalent to the binary weight of the bit (in this case 1, because  $2^0=1$ ). The command would be \*ESE 1. When and if bit zero of the standard event register is set, this bit is "ANDed" with bit zero of the standard event enable register. If both event and enable bits are set, a one is sent to bit five of the status byte. This holds true for any bit of the standard event register, since the bits resulting from "bitwise ANDing" the event register with the enable register are then "ORed".

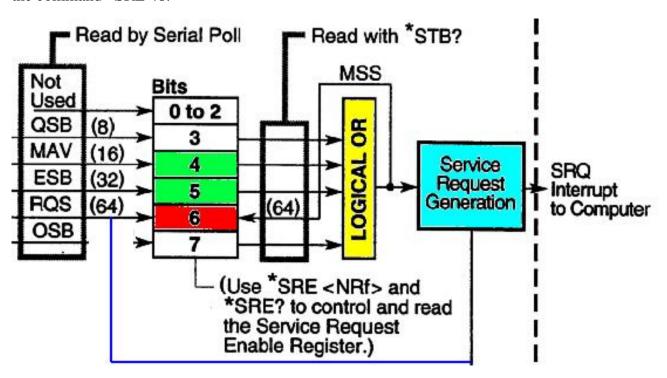

In order to achieve our goal of asserting an SRQ, the Status Byte has to be enabled. We can do this by writing the decimal sum of the binary weight of the bits we want to enable. In this case we wish to enable bits four and five. Bit 4 has a binary weight of 16 (2^4=16) and bit five has a binary weight of 32 (2^5=32). The sum is 48. So we will send

the command \*SRE 48.

When and if bits four and five get set, they will be "ANDed" with the corresponding bits of the status enable register. If any bit of the status register is set and its counterpart in the status enable register is also set, bit six of the status register will be set, causing the GPIB bus to assert an SRQ.

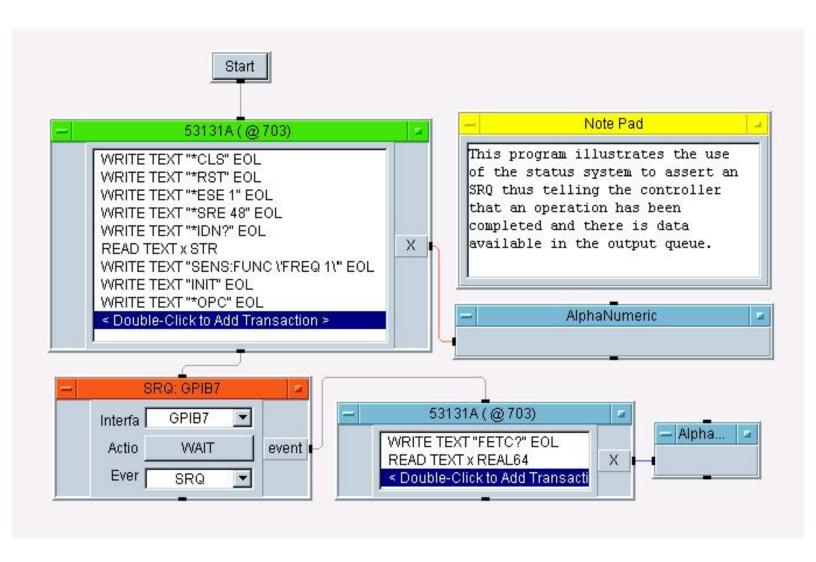

We have not yet discussed how to get the "operation complete" bit (bit 0 of the standard event register) to "set". This cannot happen without some way of identifying the operation of interest. We can do this by sending the command \*OPC after the operation of interest has been initiated. The following VEE program illustrates the entire process.

There is only one thing left to do in order to make this work. The program must have a function that either causes other operations to be delayed until the SRQ is asserted or interrupts other operations when the SRQ is asserted. The above program illustrates the use of an interface event object to cause the program to wait until the SRQ has been asserted.